3年ぶりに再会したのはいいものの、結構苦戦しているこのプロジェクト

冬休みに宿題として取り組みましたが、なかなか完成せず。

1月も終わりに近くなりまして、ようやく完成しましたので続きを告しますね。備忘録を兼ねていること、内容が結構複雑ですので、またまた内容が固くなっていることはご容赦くださいねー。

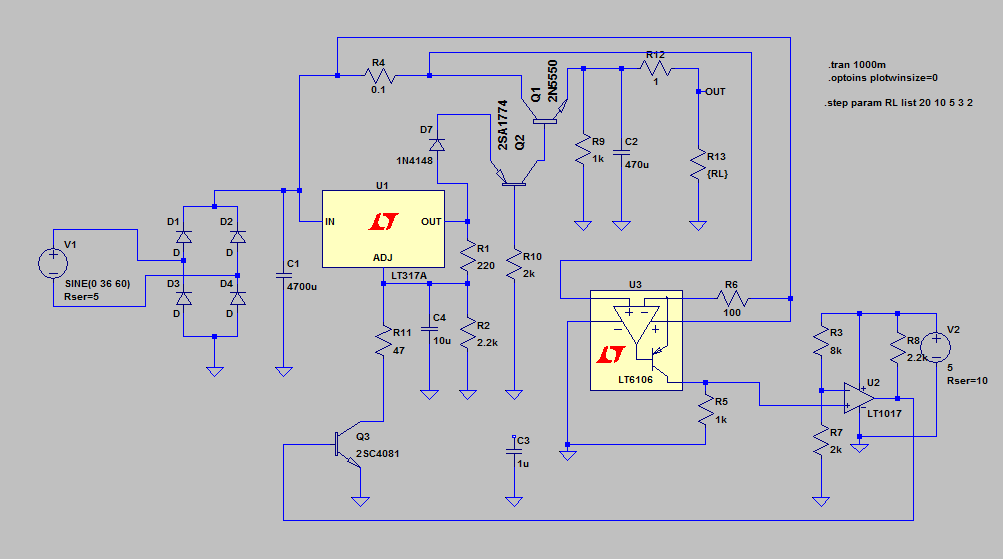

前回、手書きの回路図で進めようとしましたが、Trでブーストしていること、電流制限回路が

うまく動作するか、その辺がちょっと不安になりました。

電流制限ICがLT6106ってLinier Technorogyのデバイスを使っている関係で、今回はLTSpiceでシミュレーションしてみることにしました。

いままで、真空管シミュレーションとかを通じて、TIのTinaTIってアナログシミュレータに慣れているのですが、今回は違うシミュレータということでドキ胸胸で回路図を入力します。

最初はカットアンドトライしましたが、だいぶ最終の回路図に近くなっています。

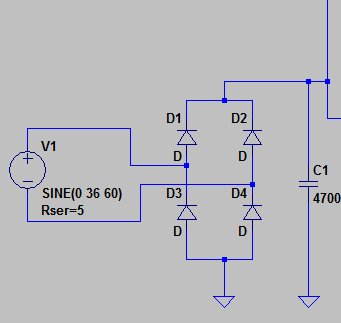

回路図を説明すると、左端は24V2Aのトランスです。

トランスがないので、電圧源でモデルを作ります。

トランスの定格の24Vは実効値なので、P-Pではルート2倍、1.4倍の36Vになります。

60Hzで、内部抵抗は適当に5Ωにしています。(2A流れると10V低下する塩梅です)

ここまでを練習でシミュレーションしてみましょう。

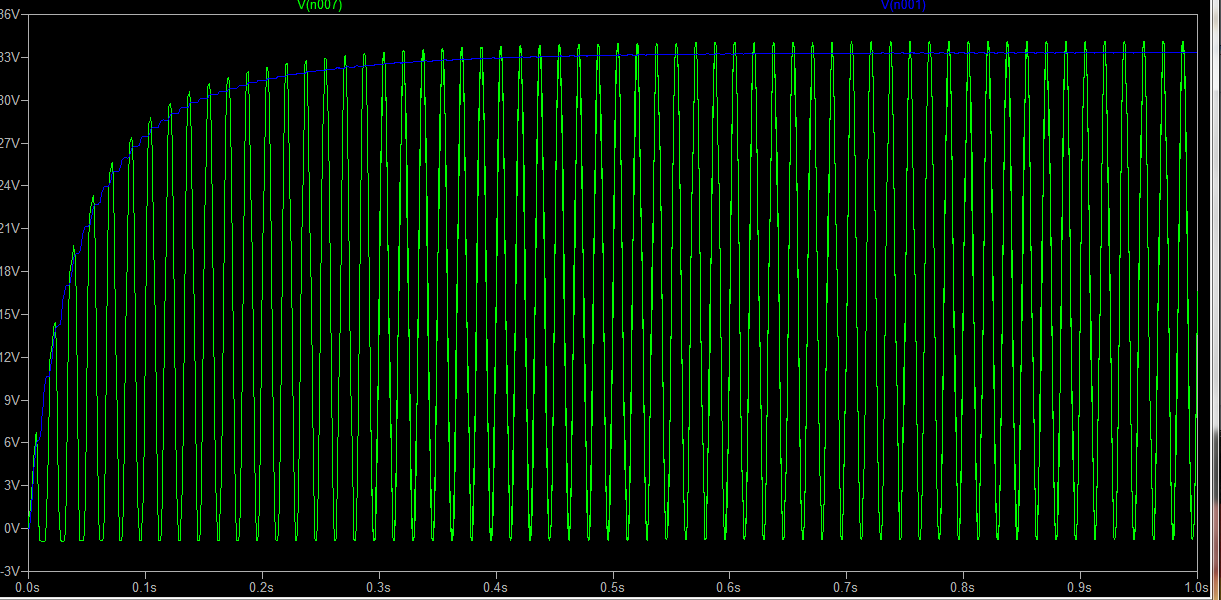

電圧源の交流電圧 約34Vとダイオードブリッジで全波整流し、C1の4700uFに現れる

電圧です。 約33Vで落ち着いていますね。

回路の拡大です。(Q2は実際は入ってません。将来のサーマルシャットダウン回路用です)

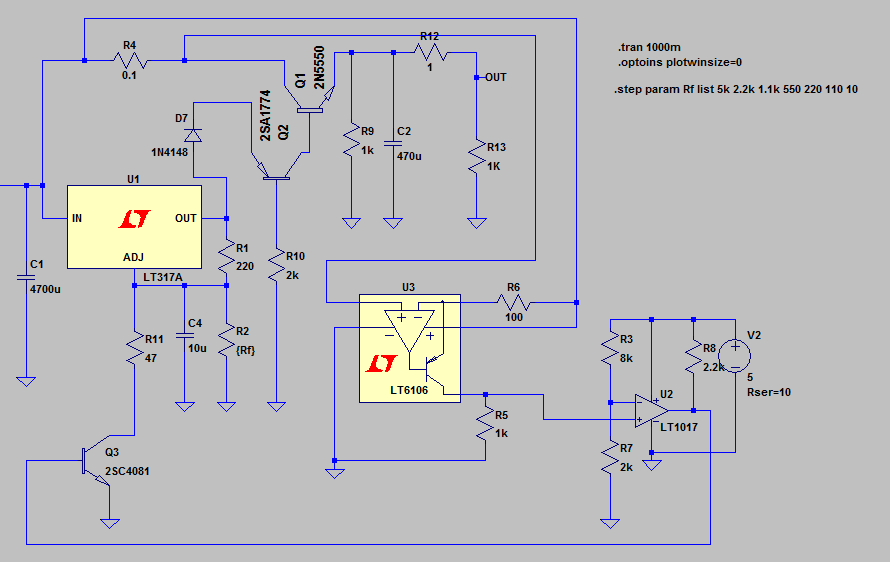

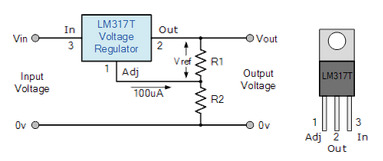

次にLM317の動作シミュレーションです。

R1の両端が1.25Vになるようにフィードバックがかかります。

R1:R2=1.25V:1.25V x R2/R1 という電圧がVoutに出力されるわけです。

今回の回路は、R1=220Ωですから、R2=2.2KΩで12.5Vが出力されます。

5KΩでは約26Vになりますよね。 でもトランスの内部抵抗があるので、負荷がかかった

ときは出力電圧が低下して26Vまで出力できるかは分かりません。

これは、最初に定義した内部抵抗5Ωが実際はどうか、ってことですよね。

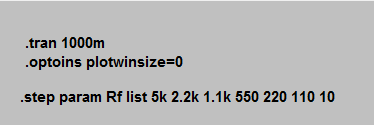

一応、R2をステップシミュレーションで可変させて、負荷が1KΩ (24Vで24mA)の軽負荷で確認してみましょう。

R2をRfってラベルで、5K、2.2k 1.1k、550Ω、220Ω、110Ω、10Ωって

抵抗を連続で変えてシミュレーションします。

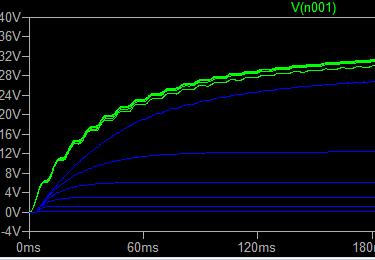

最大の5KΩで設計通り、約26V2.2Kで12.5V、最小の10Ωで0Vになっているのが

分かります。

(ブーストしているトランジスタのVbeとベースに直列のダイオードで1V位低くなります)

ダイオードとトランジスタの電圧低下の効果で、LM317Tのみで1.25V-28Vが

0V~26Vにできることが分かります。

これで、設計の負荷 2Aのときはどうなるでしょうか?

また、電流検出ICLT6106を使った電流制限回路の動作は?

この辺は、また次回ですね。

ヨッパで真面目な記事を書いているので、頭がクラクラしてきましたw

それでは、おやすみなさい

![【電子工作】実験用 可変安定化DC電源 自作プロジェクトが再起動! [Part 3]](https://powpher.com/wp/wp-content/uploads/2022/04/cropped-DSCF0454.jpg)